Nat. Electron.:基于二维异质结和光诱导俘获的可重构晶体管和存储器

2023-10-30

811

利用CMOS技术制造的场效应晶体管(FET)的缩放正接近其物理极限。这导致了对具有新结构晶体管的探索。可重构场效应晶体管(RFET)是一个很有前途的选择,因为它在工作时的可重构极性(即n型和p型模式之间的动态转换)可用于简化电路和减少实现逻辑功能所需的晶体管数量。与由物理掺杂决定的典型晶体管的固定极性不同,RFET允许选择电子或空穴注入到基于源/漏区域可调肖特基势垒的双极性沟道中,从而实现可逆极性操作。器件数量的减少也缓解了高器件封装密度的要求,降低了电子制造的复杂性。RFET的潜力已经在各种纳米线系统中得到了证明。用小带隙、2D材料作为半导体沟道的RFET也被提出。然而,这些RFET中基于极性的操作的依赖于恒定外部电压供应来诱导静电栅控场,这会导致额外的功耗和器件可靠性问题。近年来,由于铁电材料在没有外电场的情况下会发生自发极化,因此已被用作RFET的介质,用于沟道电导的非易失性调制。然而,退极化场和高栅漏电流的影响阻碍了基于铁电材料的RFET的发展。商业化面临的其他挑战包括大尺寸、短保留时间和有限的可区分状态数量。有鉴于此,近日,台湾国立清华大学Po-Wen Chiu,国立中兴大学Yen-Fu Lin和Jiunn-Lin Wu(共同通讯作者)等合作报道了一种基于hBN/ReSe2/hBN异质结的可重构FET,具有非易失性和可调极性。利用光诱导俘获机制驱动光激发空穴或电子进入hBN和二氧化硅衬底之间的界面。可重构FET可以在晶体管和存储器模式之间切换,并且几个FET可以用来构建反相器,AND,OR,NAND,NOR,XOR和XNOR电路。研究还表明,当在存储器模式操作时,该器件可用于模拟突触功能,用于神经形态计算系统。文章以“A reconfigurable transistor and memory based on a two-dimensional heterostructure and photoinduced trapping”为题发表在顶级期刊Nature Electronics上。

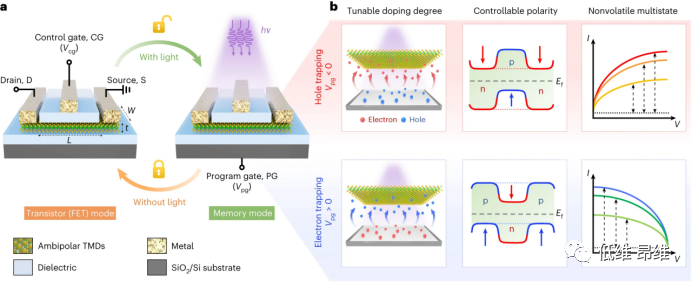

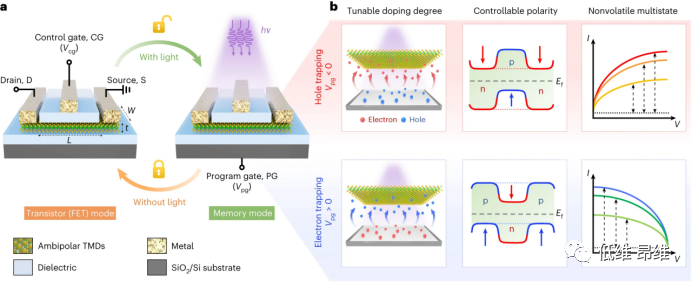

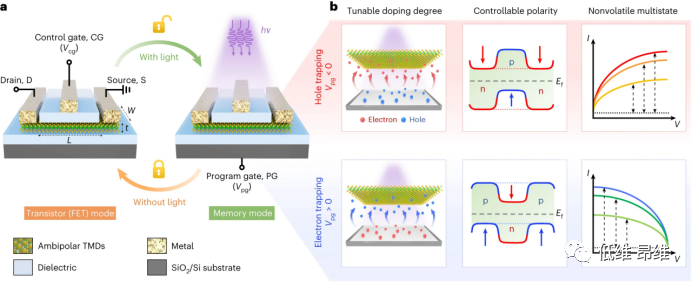

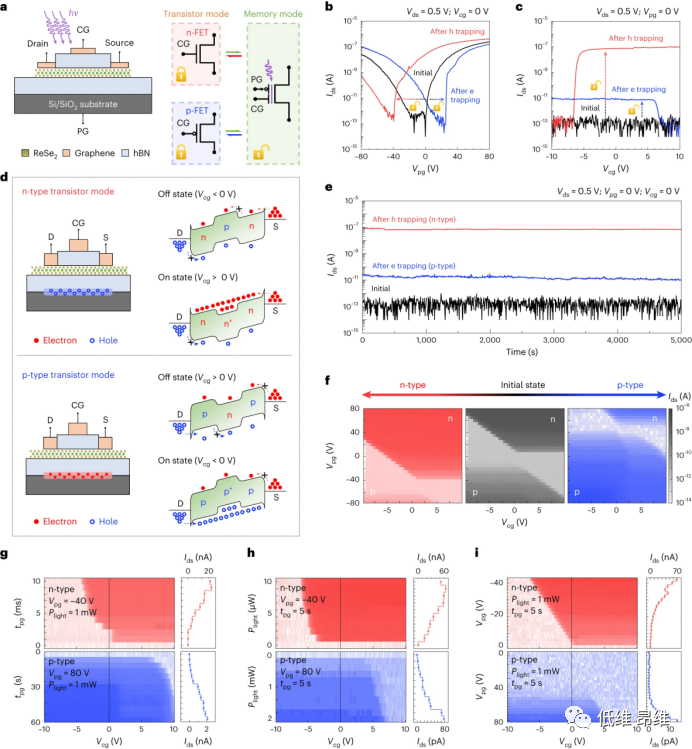

图1. 器件结构及其功能特点。(a)PT-RFET异质结器件的示意图。(b)可以在PT-RFET中实现的可调掺杂程度,n/p极性控制和非易失性多态特性的示意图。PT-RFET器件的示意图如图1a所示。主要核心由夹在SiO2/Si衬底上两个hBN电介质之间的双极性过渡金属硫族化合物(TMD)沟道组成。本文的PT-RFET结构类似于传统的RFET,除了增加了光敏电荷俘获层。这使得器件功能的非易失性编程成为可能。此外,光诱导俘获机制提供了多个可调参数,如光持续时间、功率、频率和光斑大小,用于控制器件性能。通过同时施加光照和编程栅极(Vpg)提供的负电场,TMD沟道可以从p型调制到n型,并在两种激活都被去除后保持其极性。如果正Vpg与光照结合使用,沟道极性将恢复为p型。通过控制栅极(Vcg)检测PT-RFET的特性。在两种电荷极性调制下,PT-RFET可以在晶体管模式和存储器模式之间可逆转换,从而显示出双模式优势:例如可调的掺杂程度,n/p极性控制和非易失性多态,如图1b所示。光照作为不可编程(即晶体管)模式和可编程(即存储器)模式之间转变的开关键,从而为复杂的封装制造工艺和简化集成电路提供了一种不同的方法。

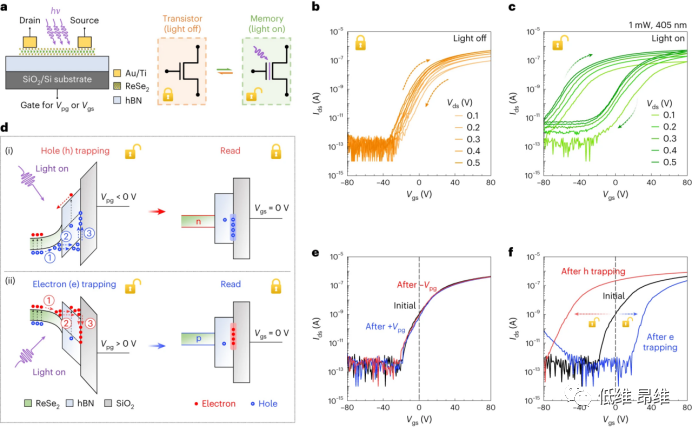

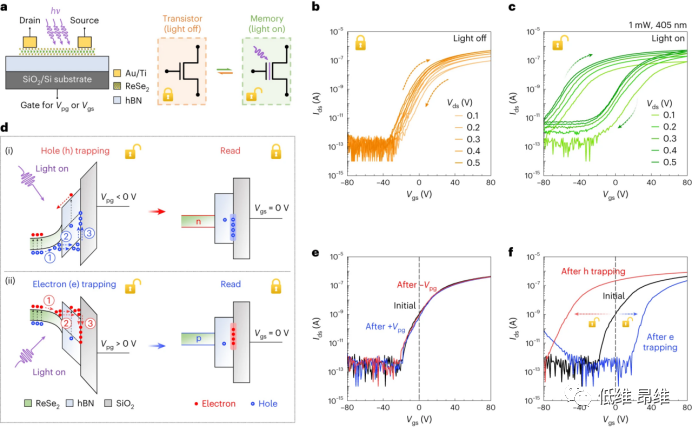

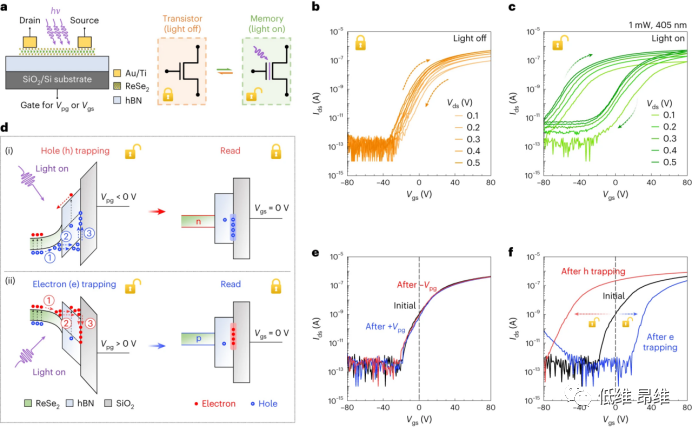

图2. ReSe2/hBN堆叠中的非易失性光诱导俘获。(a)ReSe2/hBN堆叠器件和由光照触发的晶体管-存储器切换的示意图。(b&c)黑暗条件和光照下不同Vds值的转移特性。(d)在(i)负和(ii)正Vpg光照下,hBN/SiO2界面和hBN层光诱导俘获过程的能带示意图。(e&f)在无光照和有光照条件下施加Vpg后Vds=0.5 V时堆叠器件的转移特性。为了演示可编程非易失性PT-RFET概念,本文首先制造了一个基于ReSe2/hBN堆叠的器件结构,具有传统的三端结构(图2a)。有/无光照下,器件可以在晶体管和存储器功能之间交替。在各种源漏电压(Vds)条件下,扫描背栅电压(Vgs),监测了ReSe2/hBN堆叠的电学特性。在没有光照的情况下,转移特性没有观察到迟滞(图2b)。然而,当堆叠器件暴露在持续的中等光照(1 mW,405 nm)下时,转移行为完全改变。从图2c可以看出,在Vgs=±80 V时,双扫描转移曲线的迟滞可以增加到~60 V。在有无光照的情况下,转移曲线之间的这种对比是PT-RFET中实现可编程和非易失性功能的原因。通过考虑hBN/SiO2界面的电荷俘获/去俘获以及hBN中缺陷态的存在,可以理解光照下的光致响应,如图2d所示,其方式与传统的电荷俘获型浮栅场效应管类似。在光照下,在ReSe2沟道中产生光激发的电子-空穴对。在负(正)Vpg的作用下,被激发的空穴(电子)将隧穿hBN层,并在hBN/SiO2界面处被俘获。这些被俘获在hBN/SiO2界面上的空穴(电子)会被永久俘获,直到施加另一个Vpg,静电作用导致ReSe2沟道为非易失性n型(p型)。对于hBN中的缺陷态,电荷流的输运机制与界面俘获情况略有不同。中间带隙类施主缺陷态在hBN中自然发生。在负Vpg的光照下,来自hBN缺陷态的电子被激发到其导带并向ReSe2沟道漂移。hBN中剩余的正离子作为有效的局域栅极,增强了ReSe2的n型调制。然而,在光照射和正Vpg的作用下,hBN中的激发态电子漂移到hBN/SiO2界面的陷阱态并保持在陷阱态内。这抵消了hBN中剩余的正离子,导致弱p型掺杂。图2e和f显示了Vds=0.5 V时,在没有Vpg(-80 V或80 V)和光照(5 s,1 mW,405 nm)的情况下,ReSe2/hBN堆叠的转移特性。红线和蓝线分别表示施加负和正Vpg后的转移特性,黑线表示未施加PT过程的初始电导率。如图2e所示,无论是否施加Vpg,所有曲线都紧密重合。相反,在光照后,堆叠器件的导电极性在负Vpg时变为n型,在正Vpg时变为p型,这归因于PT行为(图2f)。因此,在施加负和正Vpg之间观察到不对称的掺杂行为,这可以用hBN缺陷态中载流子锚定的不同调制要求来解释。在光照下,在正Vpg下也观察到p型区电导率的轻微变化,这是由于ReSe2的双极性性质。

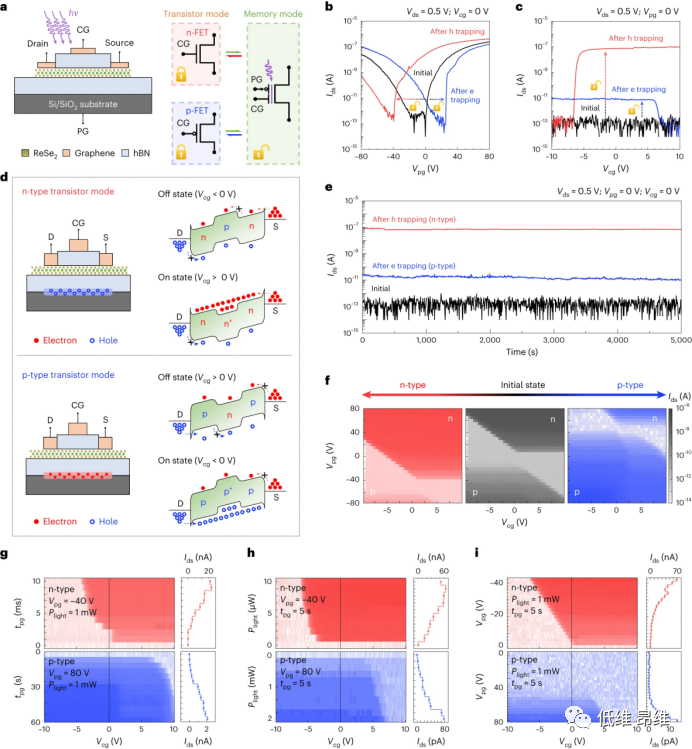

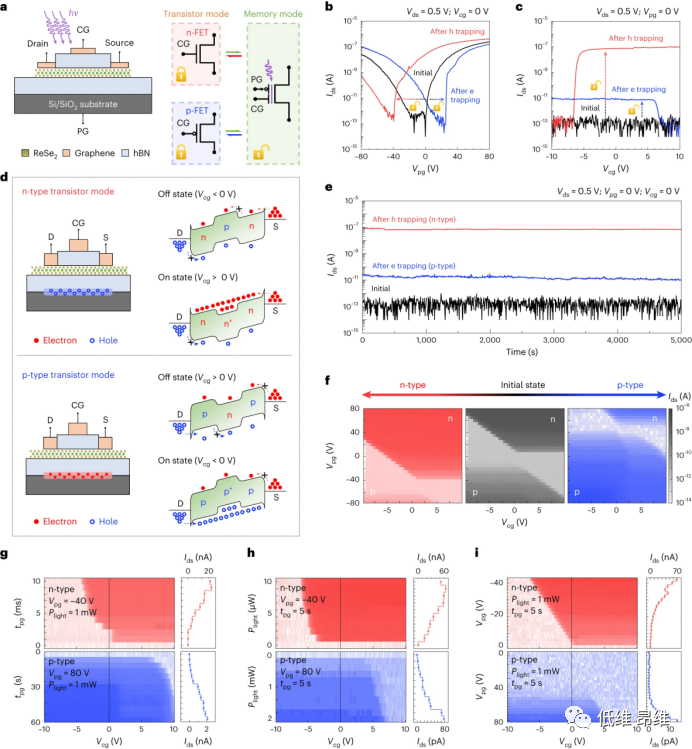

图3. PT-RFET中可重构晶体管-存储器操作的演示。(a)全2D PT-RFET及其模式转变过程的示意图。(b&c)Vds=0.5 V时传递特性与Vpg和Vcg的关系。(d)在光诱导俘获过程后的Vcg操作过程中,PT-RFET的能带示意图。(e)在Vds=0.5 V下保持5000 s。(f)在各种Vpg和Vcg条件下,Vds=0.5 V处的Ids成像。(g-i)在不同的光诱导俘获参数下,Vds=0.5 V处的Ids成像与Vcg的关系。利用非易失性堆叠器件的PT工作机制,本文展示了PT-RFET的结构和电学性质,以实现可重构的晶体管-存储器操作。图3a显示了具有全2D双栅异质结的PT-RFET,其中控制栅极被配置为部分覆盖双极性ReSe2沟道并控制开关电流调制(即晶体管模式操作),而编程栅极可以控制整个PT-RFET器件以俘获hBN/SiO2界面处的光激发空穴或电子,从而产生非易失性电荷极性(即存储器模式操作)。石墨烯用于形成源/漏/顶栅接触,两者都为光照提供透明电极,也有助于实现双极性ReSe2行为,用于RFET操作。所有器件都是通过机械剥离和牺牲层辅助堆叠方法制备的。全2D薄片厚度通常小于10 nm。图3b和c给出了一个非易失性可重构PT-RFET在经过PT过程后的转移特性与Vpg和Vcg的关系。在1 mW,405 nm光照射5 s后,随着施加负Vpg值和正Vpg值,转移曲线分别向负和正向偏移(图3b),这表明PT-RFET实现了n/p极化。由于ReSe2沟道顶部的石墨烯接触,图3b显示了明显的双极性行为,表明大多数载流子要么是电子,要么是空穴。较大的阈值电压是由于使用了较厚的SiO2电介质,并且可以通过集成高介电常数材料大大降低。然而,当Vcg从-10 V扫描到10 V时,转移特性与双极性特性完全不同,PT-RFET被设置为晶体管模式,呈现单极性行为(图3c)。这些PT-RFET的开/关电流比和n/p掺杂浓度由俘获空穴/电子的数量决定,这些空穴/电子的数量强烈依赖于Vpg的大小、编程时间(tpg)和光功率(Plight)。图3d为PT过程后施加Vcg下PT-RFET的能带示意图。首先,在hBN/SiO2界面空穴(电子)俘获条件下,ReSe2沟道可以实现高n型(p型)导通状态,对应于同时存在负(正)Vpg和光照激活。在PT-RFET的n型(p型)晶体管模式下,当Vcg<0 V(Vcg>0 V)时,ReSe2沟道中间的能带图向上(向下)弯曲,形成n-p-n(p-n-p)结构,沟道中间的势垒实质上阻碍了电子(空穴)流动,表明处于“关闭”状态。当施加Vcg>0 V(Vcg<0 V)时,中间沟道能带图向下(向上)弯曲,产生n-n+-n(p-p+-p)结构,表现为“导通”状态(图3d)。因此,通过PT-RFET的电流可以由Vcg控制,类似于传统的FET。PT-RFET的极化类型可以通过光和Vpg激活来编程,而Vcg控制其开关电流调制。在实际器件应用中,长保持保留时间和高开关电流比对于确保PT-RFET的可靠性至关重要。图3e给出了PT-RFET的数据保留能力。n和p型状态分别在Vpg=-40 V和80 V下独立工作,光照时间为5 s(1 mW,405 nm)。在Vcg=0 V和Vds=0.5 V时产生与时间无关的电流,显示n型和p型PT-RFET的开/关电流比分别高达106和102,在5×103 s内没有衰减。在长期监测下,这些PT-RFET中载流子类型的极化稳定性至少可以保持三个月。PT-RFET的优异保留性能证明了hBN/SiO2界面的非易失性电荷俘获能力和可忽略不计的电荷损失。进一步的n/p极化演示(Ids成像)如图3f所示,揭示了PT-RFET在各种Vpg和Vcg条件下的全部工作特性。此外,图3g-i显示了Vds=0.5 V时,不同PT参数下的Ids成像与Vcg的关系。这是因为在不同PT参数下,hBN/SiO2界面上俘获的空穴/电子数量是控制PT-RFET工作的关键因素。更大的tpg、Plight和Vpg值导致更高的光吸收和载流子俘获特性。

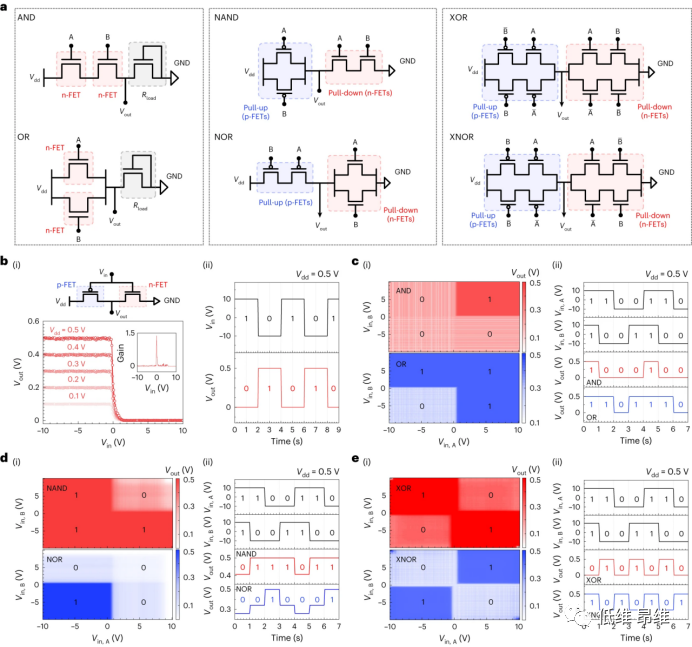

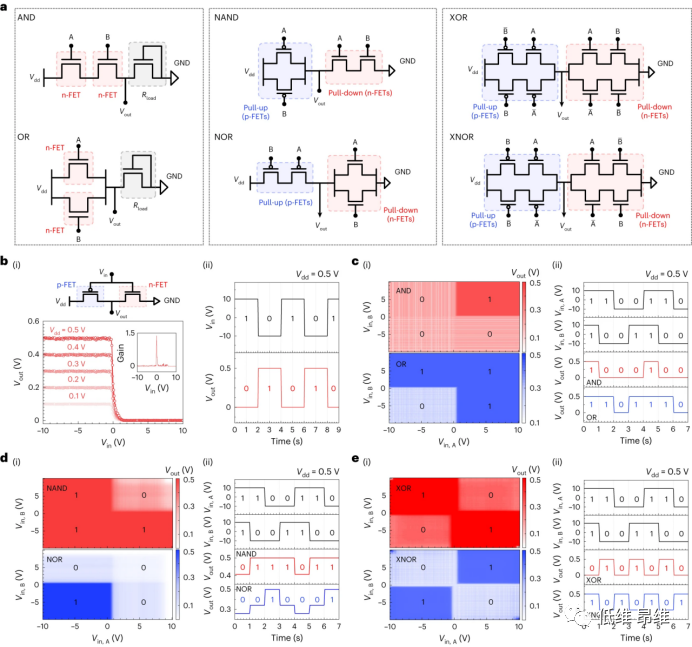

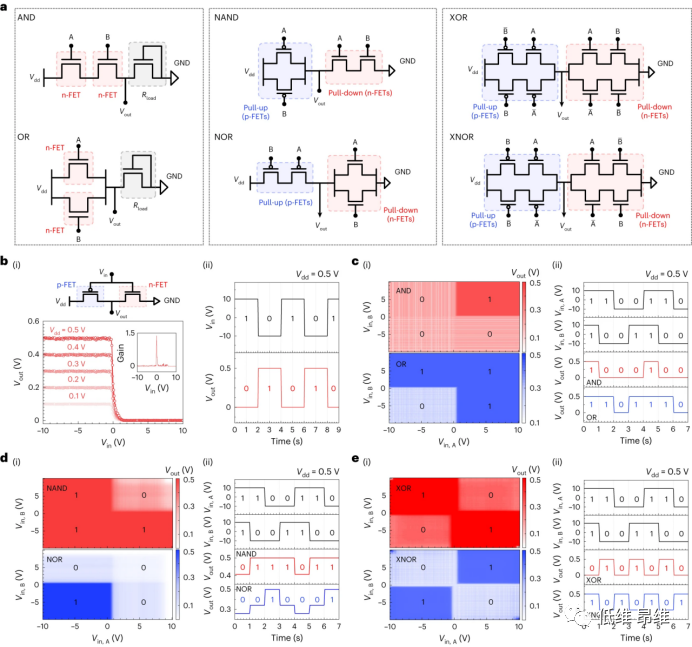

图4. 门逻辑电路的演示。(a)AND/OR、NAND/NOR和XOR/XNOR门逻辑电路的原理图。(b)由两个不同极性PT-RFET组成的反相器的示意图,以及反相器在电源电压Vdd范围为0.1至0.5 V时的电压传输特性Vout与Vin。(c-e)Vdd=0.5 V时Vout仿真结果及对应波形与Vin,A和Vin,B的关系;本文设计的PT-RFET可以用作构建基本逻辑电路的模块,展示它们在简化电子制造过程复杂性方面的优势(图4a)。AND和OR门由一对n-FET和一个电阻组成。NAND和NOR门使用两个p-FET和两个n-FET,而XOR和XNOR门将四个p-FET和四个n-FET组合成一个电路。p-FET和n-FET组分别代表上拉和下拉网络。每个单元的极性使用其控制栅极电压(由输入A和B表示)单独控制,从而符合布尔函数的操作原理。图4b显示了互补反相器的实验结果,该反相器使用两个对称且相反极性的PT-RFET(n-FET和p-FET)组装而成,代表了最基本的逻辑单元。由于成功抑制了截止状态电流,反相器在不同电源电压(Vdd)下显示出充分的输出波动,并且由于在n-FET和p-FET模式下使用时PT-RFET的对称器件特性,也显示出高度对称的特性。基于反相器功能的演示,本文进一步建立了极性可控的PT-RFET如何用于复制类CMOS门逻辑电路。当Vdd=0.5 V时,AND/OR、NAND/NOR和XOR/XNOR门逻辑电路的模拟输出结果分别如图4c-e所示。请注意,PT-RFET的编程栅极在上述电路中没有使用,而逻辑输入A和B是通过晶体管的控制栅极输入的,从而说明了本文设计与传统RFET之间的区别,并展示了PT-RFET在晶体管模式操作中的功能。

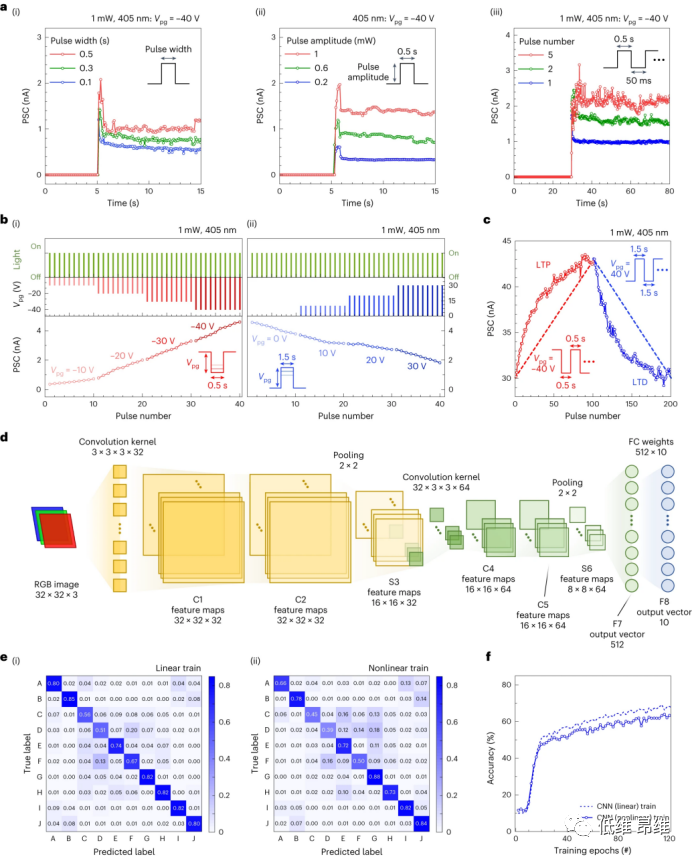

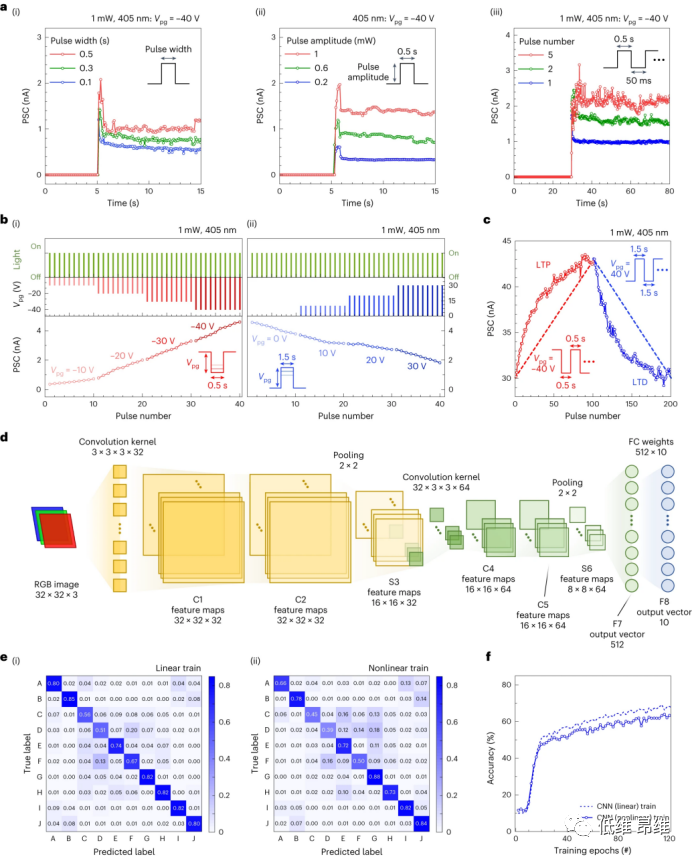

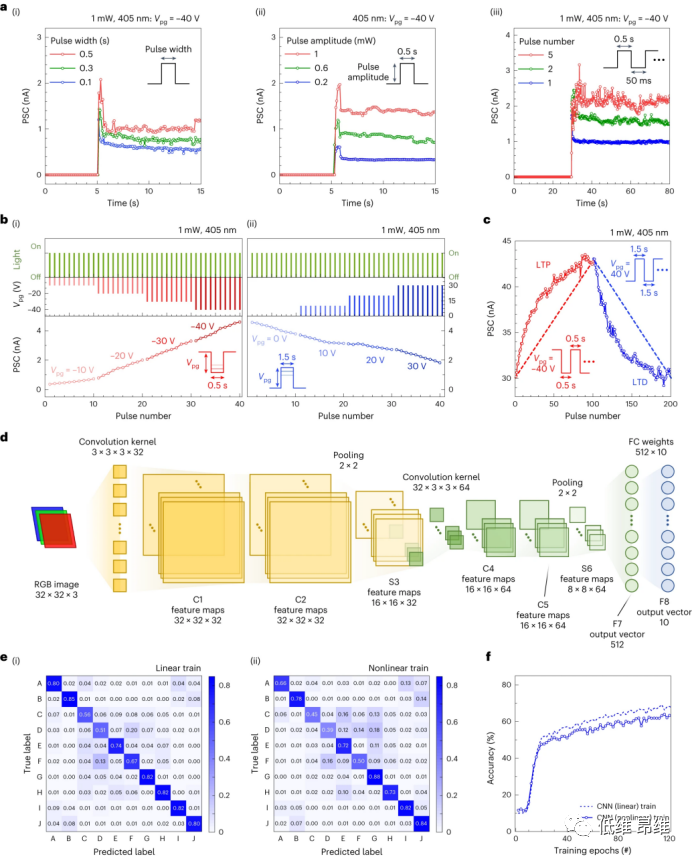

图5. 人工突触功能的演示。(a)不同(i)Vpg脉冲宽度,(ii)光幅度和(iii)脉冲数下PSC响应的变化。(b)当Vpg被逐步调节时,PSC响应与周期数的关系。(c)在Vds=0.5 V连续施加一系列增强尖峰和抑制尖峰时,PSC响应与输入尖峰数量的关系。(d)用于CIFAR-10图像识别的八层卷积神经网络架构。(e)(i)线性和(ii)非线性训练模型的混淆矩阵。(f)模拟识别准确率与训练次数的关系。PT-RFET还能够以存储器模式操作,实现可重构的神经形态功能,从而为实现复杂的生物学习和灵活的可塑性提供了一种途径。在基本的神经形态计算单元中,突触代表两个神经元之间的物理连接。突触的连接强度可以通过释放/运输化学神经递质来改变,从前神经元到后神经元。突触前和突触后峰值时间间隔的变化在决定化学神经递质数量方面起着重要作用。相应地,这种生物现象可以被类比PT-RFET中的光和电激活,因为PT过程中,施加Vpg和光照组合的输入信号被视为触发突触后电流(PSC)的前神经元的输入尖峰,相应的ReSe2沟道电导是突触权重。为了模拟两个相邻神经元细胞之间生物突触中的信息传递,本文检测了PT-RFET的PSC响应,并可以通过改变Vpg脉冲宽度、光振幅和脉冲数进行修改,如图5a(i)-(iii)所示。较大的Vpg脉冲宽度、光振幅和脉冲数可以在hBN/SiO2界面上产生更多的空穴/电子,然后激活PSC变化,从而驱动神经形态计算的突触权重。在PT过程中,连续Vpg脉冲进一步作为突触前输入信号来检测动态增强和抑制行为。图5b(i)中监测到的PSC通过改变10脉冲负Vpg序列逐渐增加到4.59 nA,然后通过施加正Vpg脉冲序列降低到1.82 nA(图5b(ii))。负和正Vpg调谐的PSC响应显示了PT-RFET的柔性可塑性,分别对应于hBN/SiO2界面上发生的持续空穴和电子俘获。利用通过PT过程获得的能力,将100个Vpg=-40 V(1 mW,405 nm,0.5 s持续时间,0.5 s脉冲间隔)的负脉冲施加到PT-RFET上,然后施加100个Vpg=40 V(1 mW,405 nm,1.5 s持续时间,1.5 s脉冲间隔)的正脉冲,如图5c所示。在Vpg极性为负/正的连续激活下,PSC的突触可塑性可以调节,表现出增加(增强)/减少(抑制)特征。观察到的PSC变化特征是生物系统的关键行为,即脉冲数依赖的长时程增强和抑制,验证了全2D PT-RFET用作人工突触的潜力。基于卷积神经网络(CNN)的计算可以替代用于传统计算机的冯·诺伊曼设计,从而提高数据处理效率。基于实验观察到的PT-RFET的增强/抑制行为(图5c),本文构建了一个八层CNN来识别CIFAR-10图像,使用PT-RFET作为深度神经网络的硬件(图5d)。图5e(i)和(ii)给出了对线性(理想)和非线性(实验)特征进行混淆矩阵识别的仿真结果。相应的识别准确率与训练时期数的关系如图5f所示。经过120次训练后,线性和非线性特征的准确率分别达到73%和68%左右。理想条件和实验条件之间的差异非常小,表明本文提出的PT-RFET具有作为边缘计算和神经形态应用硬件的潜力。在器件层面的突触功能仿真和在系统层面的CNN仿真表明,本文设计的全2D PT-RFET在模式识别任务中可以实现高性能。本文报道了一种基于hBN/ReSe2/hBN异质结的PT-RFET,它可以执行可重构和可切换的多功能逻辑和神经形态操作。利用PT机制,可以以可逆且非易失性的方式控制hBN/SiO2界面上俘获的空穴/电子的数量,从而控制器件沟道掺杂构型。这导致PT-RFET在电荷极性方面具有多种不同的输运机制。与其他RFET相比,光诱导激活机制通过光脉冲特性(如持续时间、功率、频率和光斑大小)提供了额外的控制程度来调节掺杂。PT-RFET可以用作可重构单元,简化逻辑电路的复杂性。通过将PT-RFET单元级联到电路布局中,演示了反相器、AND、OR、NAND、NOR、XOR和XNOR功能,证明了这种方法在使用简化电路构建高级微处理器方面的潜力。PT-RFET还可以在器件层面模拟突触可塑性,在系统层面对CNN进行仿真,在理想条件和实验条件之间具有较高的精度。本文的全2D PT-RFET可用于开发高效计算硬件,信息存储和下一代固态神经形态电路,或作为当前半导体技术的附加单元。A reconfigurable transistor and memory based on a two-dimensional heterostructure and photoinduced trapping(Nat. Electron., 2023, DOI:10.1038/s41928-023-01034-7)

关键词:低维材料技术,材料技术

相关文章

吕坚院士团队《EES》:双相超纳多组元合金,突破超高活性析氢!

材料技术,科学技术

2024-10-31

北工大硬质合金:可塌缩基质辅助数字光处理实现硬质合金高精度打印

材料技术,科学技术

2024-10-31

哈工大顶刊:高温合金增减材复合制造中的显微组织和残余应力演变

材料技术,科学技术

2024-10-31